# DAS-429UNET/RTx

## **Avionics Communication Device**

# **User's Manual**

**One Step Ahead**

Copyright © 2014–2017 Excalibur Systems. All Rights Reserved.

## **Table of Contents**

| 1 | Intro                                                         | duction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1                                                           | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |                                                               | 1.1.1 Battery Option                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 1.2                                                           | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 1.3                                                           | Product Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 1.4                                                           | Supporting Software1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 1.5                                                           | Discrete Channel Information1-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 1.6                                                           | Technical Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2 | Insta                                                         | Illation and Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 2.1                                                           | Installing the Software on the Host Computer2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 2.2                                                           | Connecting the Cables2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |                                                               | 2.2.1 Connecting the DAS-429UNET/RTx Cables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

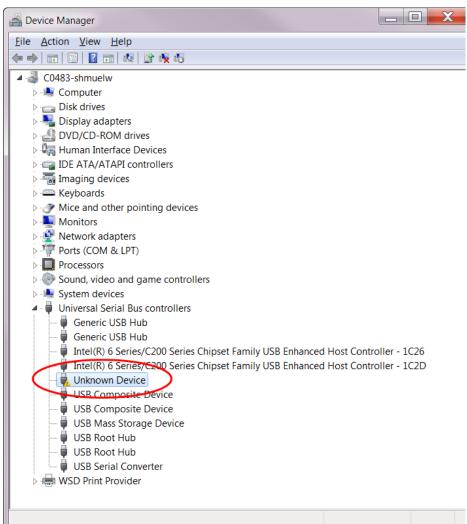

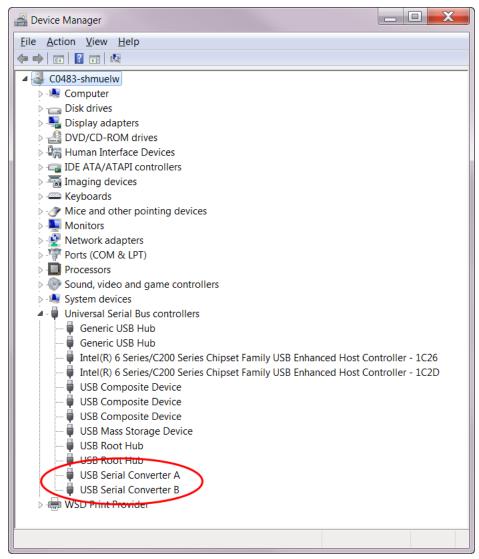

|   | 2.3                                                           | Installing the USB Driver on the Host Computer2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 2.4                                                           | Assigning a Device Number on the Host Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 2.5                                                           | Setting the UNET's Ethernet Settings2-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |                                                               | 2.5.1 Overview of Setting the UNET's Ethernet Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |                                                               | 2.5.2 Setting the Ethernet Settings via USB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 2.0                                                           | 2.5.3 Setting the Ethernet Settings via Ethernet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 2.6<br>2.7                                                    | Testing the Connection Using the Device Number.       2-25         Running a Test Program       2-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 2.7                                                           | Running the Discrete Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 2.0<br>2.9                                                    | Uninstalling the Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| • |                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3 | L)eve                                                         | Noning Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5 |                                                               | eloping Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5 | 3.1                                                           | Porting an Existing Application to Work with the UNET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| J |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4 | 3.1<br>3.2<br>Mecl                                            | Porting an Existing Application to Work with the UNET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| - | 3.1<br>3.2<br><b>Mecl</b><br>4.1                              | Porting an Existing Application to Work with the UNET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| - | 3.1<br>3.2<br>Mect<br>4.1<br>4.2                              | Porting an Existing Application to Work with the UNET       3-1         Developing New Applications for the UNET       3-3         hanical and Electrical Specifications       4-2         LED Indicators       4-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| - | 3.1<br>3.2<br><b>Mecl</b><br>4.1                              | Porting an Existing Application to Work with the UNET       .3-1         Developing New Applications for the UNET       .3-3         hanical and Electrical Specifications       .4-2         LED Indicators       .4-4         Connectors       .4-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| - | 3.1<br>3.2<br>Mect<br>4.1<br>4.2                              | Porting an Existing Application to Work with the UNET       3-1         Developing New Applications for the UNET       3-3         hanical and Electrical Specifications       4-2         LED Indicators       4-4         Connectors       4-6         4.3.1       I/O Connector       4-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| - | 3.1<br>3.2<br>Mect<br>4.1<br>4.2                              | Porting an Existing Application to Work with the UNET       3-1         Developing New Applications for the UNET       3-3         hanical and Electrical Specifications       4-2         LED Indicators       4-4         Connectors       4-6         4.3.1       I/O Connector       4-6         4.3.2       USB Communication Connector       4-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| - | 3.1<br>3.2<br>Mect<br>4.1<br>4.2                              | Porting an Existing Application to Work with the UNET3-1Developing New Applications for the UNET3-3hanical and Electrical Specifications4-2LED Indicators4-4Connectors4-64.3.1I/O Connector4-64.3.2USB Communication Connector4-84.3.3USB Power Connector4-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| - | 3.1<br>3.2<br>Mect<br>4.1<br>4.2                              | Porting an Existing Application to Work with the UNET3-1Developing New Applications for the UNET3-3hanical and Electrical Specifications4-2LED Indicators4-4Connectors4-64.3.1I/O Connector4-64.3.2USB Communication Connector4-84.3.3USB Power Connector4-84.3.4Ethernet Connector4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| - | 3.1<br>3.2<br>Mecl<br>4.1<br>4.2<br>4.3                       | Porting an Existing Application to Work with the UNET3-1Developing New Applications for the UNET3-3hanical and Electrical Specifications4-2LED Indicators4-4Connectors4-64.3.1I/O Connector4-64.3.2USB Communication Connector4-84.3.3USB Power Connector4-84.3.4Ethernet Connector4-94.3.5External Signals Connector Pinouts4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| - | 3.1<br>3.2<br>Mect<br>4.1<br>4.2                              | Porting an Existing Application to Work with the UNET3-1Developing New Applications for the UNET3-3hanical and Electrical Specifications4-2LED Indicators4-4Connectors4-64.3.1I/O Connector4-64.3.2USB Communication Connector4-84.3.3USB Power Connector4-84.3.4Ethernet Connector4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| - | 3.1<br>3.2<br>Mecl<br>4.1<br>4.2<br>4.3                       | Porting an Existing Application to Work with the UNET3-1Developing New Applications for the UNET3-3hanical and Electrical Specifications4-2LED Indicators4-4Connectors4-64.3.1I/O Connector4-64.3.2USB Communication Connector4-84.3.3USB Power Connector4-84.3.4Ethernet Connector4-94.3.5External Signals Connector Pinouts4-94.4.1Battery Information (Battery Option Only)4-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4 | 3.1<br>3.2<br>Mecl<br>4.1<br>4.2<br>4.3                       | Porting an Existing Application to Work with the UNET3-1Developing New Applications for the UNET3-3hanical and Electrical Specifications4-2LED Indicators4-4Connectors4-64.3.1I/O Connector4-64.3.2USB Communication Connector4-84.3.3USB Power Connector4-84.3.4Ethernet Connector4-94.3.5External Signals Connector Pinouts4-94.4.1Battery Information (Battery Option Only)4-13t Interface Global Registers (Advanced)4-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4 | 3.1<br>3.2<br>Mecl<br>4.1<br>4.2<br>4.3<br>4.4<br>Host        | Porting an Existing Application to Work with the UNET       .3-1         Developing New Applications for the UNET       .3-3         hanical and Electrical Specifications       .4-2         LED Indicators       .4-4         Connectors       .4-6         4.3.1       I/O Connector       .4-6         4.3.2       USB Communication Connector       .4-8         4.3.3       USB Power Connector       .4-8         4.3.4       Ethernet Connector       .4-9         4.3.5       External Signals Connector Pinouts       .4-9         Power Requirements for UNET       .4-13         4.4.1       Battery Information (Battery Option Only)       .4-13         t Interface Global Registers (Advanced)       .5-2         Host Interface Global Registers Map       .5-3                                                                                                                                                                                                                                                                                                                        |

| 4 | 3.1<br>3.2<br>Mecl<br>4.1<br>4.2<br>4.3<br>4.4<br>Host        | Porting an Existing Application to Work with the UNET.3-1Developing New Applications for the UNET.3-3hanical and Electrical Specifications.4-2LED Indicators.4-4Connectors.4-64.3.1I/O Connector.4-64.3.2USB Communication Connector.4-84.3.3USB Power Connector.4-84.3.4Ethernet Connector.4-94.3.5External Signals Connector Pinouts.4-9Power Requirements for UNET.4-134.4.1Battery Information (Battery Option Only).4-134.1Board Identification Registers Map.5-25.1.1Board Identification Register.5-35.1.2Software Reset Register.5-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4 | 3.1<br>3.2<br>Mecl<br>4.1<br>4.2<br>4.3<br>4.4<br>Host        | Porting an Existing Application to Work with the UNET       3-1         Developing New Applications for the UNET       3-3         hanical and Electrical Specifications       4-2         LED Indicators       4-4         Connectors       4-6         4.3.1       I/O Connector       4-6         4.3.2       USB Communication Connector       4-8         4.3.3       USB Power Connector       4-8         4.3.4       Ethernet Connector       4-9         4.3.5       External Signals Connector Pinouts       4-9         Power Requirements for UNET.       4-13         4.4.1       Battery Information (Battery Option Only)       4-13         tInterface Global Registers (Advanced)       4-9         Host Interface Global Registers Map       5-3         5.1.2       Software Reset Register       5-3         5.1.3       Channel Info Registers       5-3                                                                                                                                                                                                                           |

| 4 | 3.1<br>3.2<br>Mecl<br>4.1<br>4.2<br>4.3<br>4.4<br>Host        | Porting an Existing Application to Work with the UNET       3-1         Developing New Applications for the UNET       3-3         hanical and Electrical Specifications       4-2         LED Indicators       4-4         Connectors       4-6         4.3.1       I/O Connector       4-6         4.3.2       USB Communication Connector       4-8         4.3.3       USB Power Connector       4-8         4.3.4       Ethernet Connector       4-9         4.3.5       External Signals Connector Pinouts       4-9         Power Requirements for UNET       4-13         4.4.1       Battery Information (Battery Option Only)       4-13         t Interface Global Registers (Advanced)       5-2         Host Interface Global Registers Map       5-3         5.1.2       Software Reset Register       5-3         5.1.3       Channel Info Registers       5-3         5.1.4       Time Tag Clock Select Register       5-3                                                                                                                                                              |

| 4 | 3.1<br>3.2<br>MecH<br>4.1<br>4.2<br>4.3<br>4.4<br>Host<br>5.1 | Porting an Existing Application to Work with the UNET       3-1         Developing New Applications for the UNET       3-3         hanical and Electrical Specifications       4-2         Mechanical Outline       4-2         LED Indicators       4-4         Connectors       4-6         4.3.1       I/O Connector       4-6         4.3.2       USB Communication Connector       4-8         4.3.3       USB Power Connector       4-8         4.3.4       Ethernet Connector       4-9         4.3.5       External Signals Connector Pinouts       4-9         Power Requirements for UNET       4-13         4.4.1       Battery Information (Battery Option Only)       4-13         t Interface Global Registers Map       5-2         5.1.1       Board Identification Register       5-3         5.1.2       Software Reset Register       5-3         5.1.3       Channel Info Registers       5-3         5.1.4       Time Tag Clock Select Register       5-4                                                                                                                          |

| 4 | 3.1<br>3.2<br>Mecl<br>4.1<br>4.2<br>4.3<br>4.4<br>Host        | Porting an Existing Application to Work with the UNET       3-1         Developing New Applications for the UNET       3-3         hanical and Electrical Specifications       4-2         Mechanical Outline       4-2         LED Indicators       4-4         Connectors       4-6         4.3.1       I/O Connector       4-6         4.3.2       USB Communication Connector       4-8         4.3.3       USB Power Connector       4-8         4.3.4       Ethernet Connector       4-9         4.3.5       External Signals Connector Pinouts       4-9         Power Requirements for UNET       4-13         4.4.1       Battery Information (Battery Option Only)       4-13         4.4.1       Battery Information Registers (Advanced)         Host Interface Global Registers Map       5-2         5.1.1       Board Identification Register       5-3         5.1.2       Software Reset Register       5-3         5.1.3       Channel Info Registers       5-3         5.1.4       Time Tag Clock Select Register       5-4         IRIG B Host Interface Global Registers       5-4 |

| 4 | 3.1<br>3.2<br>MecH<br>4.1<br>4.2<br>4.3<br>4.4<br>Host<br>5.1 | Porting an Existing Application to Work with the UNET       3-1         Developing New Applications for the UNET       3-3         hanical and Electrical Specifications       4-2         Mechanical Outline       4-2         LED Indicators       4-4         Connectors       4-6         4.3.1       I/O Connector       4-6         4.3.2       USB Communication Connector       4-8         4.3.3       USB Power Connector       4-8         4.3.4       Ethernet Connector       4-9         4.3.5       External Signals Connector Pinouts       4-9         Power Requirements for UNET       4-13         4.4.1       Battery Information (Battery Option Only)       4-13         t Interface Global Registers Map       5-2         5.1.1       Board Identification Register       5-3         5.1.2       Software Reset Register       5-3         5.1.3       Channel Info Registers       5-3         5.1.4       Time Tag Clock Select Register       5-4                                                                                                                          |

|   |     | 5.2.3            | IRIG B Time SBS Low Register                       |

|---|-----|------------------|----------------------------------------------------|

|   |     | 5.2.4            | IRIG B Time Days Register                          |

|   |     | 5.2.5            | IRIG B Time Hours Register                         |

|   |     | 5.2.6            | IRIG B Time Minutes Register                       |

|   |     | 5.2.7            | IRIG B Time Seconds Register                       |

|   |     | 5.2.8            | Control Functions Registers                        |

|   |     | 5.2.9            | FPGA Revision Register                             |

|   | 5.3 | Global           | Timer Registers                                    |

|   |     | 5.3.1            | Timer Prescale Register                            |

|   |     | 5.3.2            | Timer Preload Register                             |

|   |     | 5.3.3            | Timer Control Register                             |

|   |     | 5.3.4            | General Purpose Timer Register                     |

|   |     | 5.3.5            | Board Type Register                                |

| 6 |     | JC 429           | Module Control Registers (Advanced)                |

| v | 6.1 |                  | g Started                                          |

|   | 6.2 |                  | 2 429 Module General Memory Map                    |

|   |     |                  |                                                    |

|   | 6.3 |                  | 429 Module Global Registers Memory Map             |

|   | 6.4 |                  | 429 Module Global Register Definitions             |

|   |     | 6.4.1            | Module Options Register                            |

|   |     | 6.4.2            | Interrupt Status Busy Register                     |

|   |     | 6.4.3            | Receive Merge Status Register                      |

|   |     | 6.4.4            | Receive Merge Interrupt/Trigger Condition Register |

|   |     | 6.4.5            | Receive Merge Configuration Register               |

|   |     | 6.4.6            | Receive Merge Label Trigger Register               |

|   |     | 6.4.7            | Receive Merge Error Count Register                 |

|   |     | 6.4.8            | Receive Merge Interval Count Trigger Register      |

|   |     | 6.4.9            | Receive Merge Buffer Wraparound Register           |

|   |     | 6.4.10           | Receive Merge Word Count Trigger Register          |

|   |     | 6.4.11           | Receive Merge Word Counter                         |

|   |     | 6.4.12           | Receive Merge Filter Table Start Address           |

|   |     | 6.4.13           | Receive Merge Current Pointer                      |

|   |     | 6.4.14           | Receive Merge End Pointer                          |

|   |     | 6.4.15<br>6.4.16 | Receive Merge Start Pointer                        |

|   |     | 6.4.17           | Receive Data Storage Mode Register                 |

|   |     | 6.4.17           | Programmable Bit Rate Register                     |

|   |     | 6.4.19           | Interrupt Status Register                          |

|   |     | 6.4.20           | Firmware Revision Register                         |

|   |     | 6.4.21           | Board Status Register                              |

|   |     | 6.4.22           | Board ID Register                                  |

|   |     | 6.4.23           | Start/Stop Register                                |

|   |     | 6.4.24           | Time Tag Reset Register                            |

|   |     | 6.4.25           | Software Reset Register                            |

|   |     | 6.4.26           | Time Tag Counter                                   |

|   |     | 6.4.27           | Hardware Revision Register                         |

|   |     | 6.4.28           | Channel Enable Register                            |

|   |     | 6.4.29           | Channel Type Select Register                       |

|   | 6.5 |                  | nit Channel Operation                              |

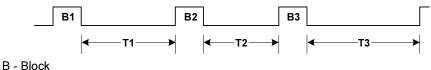

|   |     | 6.5.1            | Interblock Time Mode and Data Rate Mode            |

|   |     | 6.5.2            | FIFO Mode                                          |

|   | 6.6 |                  | ve Channel Operation                               |

|   | 0.0 | 6.6.1            | Sequential and Merge Modes                         |

|   |     | 6.6.2            | Look-up Table Mode Operation                       |

|   | 6.7 |                  | ation (Dual Channel) Operation                     |

|   | 0.7 | 1141151          |                                                    |

|      | 6.7.1            | Allocating a Translation Table in a Channel                                                           | .6-38 |

|------|------------------|-------------------------------------------------------------------------------------------------------|-------|

|      | 6.7.2            | Allocating a Translation Table Entry                                                                  | .6-38 |

|      | 6.7.3            | Using Translation Functions                                                                           | .6-38 |

| 6.8  | Chann            | el Control Registers Maps                                                                             | .6-41 |

|      | 6.8.1            | Channel 0 Control Register Block Memory Map                                                           | .6-41 |

|      | 6.8.2            | Channel 1 Control Register Block Memory Map                                                           | .6-42 |

|      | 6.8.3            | Channel 2 Control Register Block Memory Map                                                           | .6-43 |

|      | 6.8.4            | Channel 3 Control Register Block Memory Map                                                           | .6-44 |

|      | 6.8.5            | Channel 4 Control Register Block Memory Map                                                           | .6-45 |

|      | 6.8.6            | Channel 5 Control Register Block Memory Map                                                           | .6-46 |

|      | 6.8.7            | Channel 6 Control Register Block Memory Map                                                           |       |

|      | 6.8.8            | Channel 7 Control Register Block Memory Map                                                           | .6-48 |

|      | 6.8.9            | Channel 8 Control Register Block Memory Map                                                           | .6-49 |

|      | 6.8.10           | Channel 9 Control Register Block Memory Map                                                           | .6-50 |

| 6.9  | Chann            | el Control Register Definitions                                                                       | .6-51 |

|      | 6.9.1            | Channel x Scratch Buffer End Register.                                                                | .6-51 |

|      | 6.9.2            | Channel x Scratch Buffer Start Register                                                               | .6-51 |

|      | 6.9.3            | Channel x Status Register.                                                                            |       |

|      | 6.9.4            | Channel x Interrupt/Trigger Condition Register                                                        |       |

|      | 6.9.5            | Channel x Transmit Loop Counter.                                                                      |       |

|      | 6.9.6            | Channel x Transmit Instruction Counter                                                                |       |

|      | 6.9.7            | Channel x Transmit Instruction Stack Pointer                                                          |       |

|      | 6.9.8            | Channel x Receive Label Trigger Register                                                              |       |

|      | 6.9.9            | Channel x Receive Error Count Register                                                                |       |

|      | 6.9.10<br>6.9.11 | Channel x Receive Interval Counter Trigger Register                                                   |       |

|      | 6.9.12           | Channel x Receive Data Word Counter Trigger Registers<br>Channel x Receive Buffer Wraparound Register |       |

|      | 6.9.12           | Channel x Receive/Transmit Data Word Count Register                                                   |       |

|      | 6.9.14           | Channel x Receive Filter Table Start Address.                                                         |       |

|      | 6.9.15           | Channel <i>x</i> Receive Look-up Table Start Address                                                  |       |

|      | 6.9.16           | Channel x Receive Data Current Pointer                                                                |       |

|      | 6.9.17           | Channel x Receive Data End Pointer                                                                    |       |

|      | 6.9.18           | Channel x Receive Data Start Pointer.                                                                 |       |

|      | 6.9.19           | Channel x Configuration Register                                                                      |       |

| Disc | roto Ma          | odule Control Registers (Advanced)                                                                    |       |

|      |                  |                                                                                                       | 7 0   |

| 7.1  |                  | tes Module Memory Map                                                                                 |       |

| 7.2  |                  | te Control Register Definitions                                                                       |       |

|      |                  | Start Register                                                                                        |       |

|      | 7.2.2<br>7.2.3   |                                                                                                       |       |

|      | 7.2.3            | FIFO Data Register                                                                                    |       |

|      | 7.2.5            | FIFO Usage Register                                                                                   |       |

|      | 7.2.6            | FIFO Status Register.                                                                                 |       |

|      | 7.2.7            | Reset Register                                                                                        |       |

|      | 7.2.8            | Discrete Inputs [0 – 7] Interrupt Pending Register.                                                   |       |

|      | 7.2.9            | Reset Discrete Inputs [0 – 7] Interrupt Pending Register                                              |       |

|      | 7.2.10           | Interrupt on FIFO Word Count Enable Register                                                          |       |

|      | 7.2.11           | Interrupt on FIFO Word Count Value Register                                                           |       |

|      | 7.2.12           | FPGA Revision Register                                                                                |       |

|      | 7.2.13           | Discretes 0 – 7 Trigger Mask Register                                                                 |       |

|      | 7.2.14           | Discretes 0 – 7 Trigger Value Register                                                                |       |

|      | 7.2.15           | Discretes 0 – 7 Trigger on Change Register                                                            |       |

|      | 7.2.16           | Trigger Destination Register                                                                          |       |

|      | 7.2.17           | Discretes Configuration Registers                                                                     | .7-12 |

7

| 7.2.18 | Discretes 0 – 3 Configuration Registers | 7-12 |

|--------|-----------------------------------------|------|

| 7.2.19 | Discretes 4 – 7 Configuration Registers | 7-13 |

| 7.2.20 | Time Tag Hi & Lo.                       | 7-14 |

|        |                                         |      |

### 8 Ordering Information

Appendix A ARINC 429 Basic Word Formats

Appendix B ARINC 429 Connection Precautions

## Figures

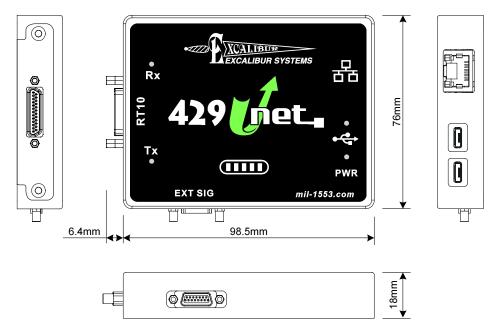

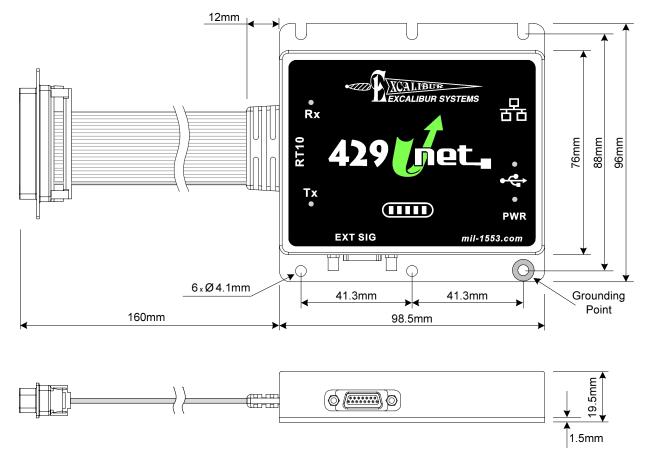

| Figure 1-1  | DAS-429UNET/RTx                                                         | 1-2    |

|-------------|-------------------------------------------------------------------------|--------|

| Figure 1-2  | DAS-429UNET/RTx Block Diagram.                                          | 1-3    |

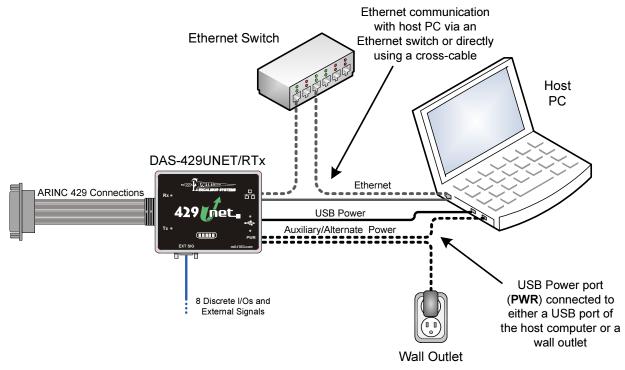

| Figure 2-1  | USB Communication with Host                                             |        |

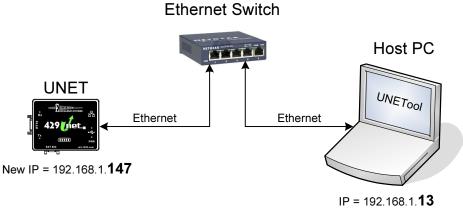

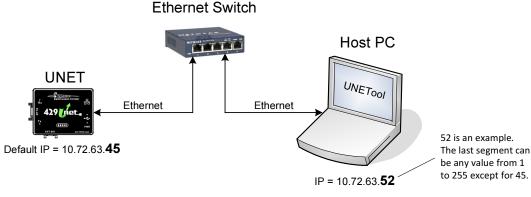

| Figure 2-2  | Ethernet Communication with Host                                        |        |

| Figure 2-6  | Demo Programs on the Start Menu                                         | . 2-28 |

| Figure 4-1  | DAS-429UNET/RTx-M                                                       |        |

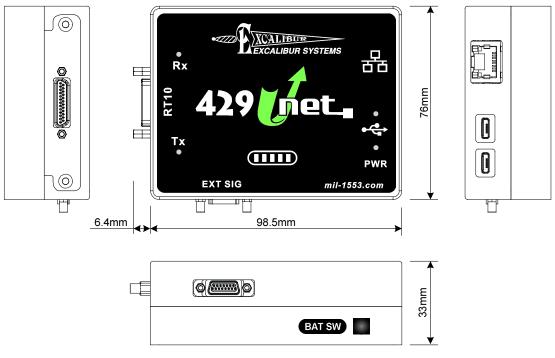

| Figure 4-2  | DAS-429UNET/RTx-M-B with Internal Battery                               | 4-2    |

| Figure 4-3  | DAS-429UNET/RTx-C-P with Hard-wired Cable and Mounting Plate            |        |

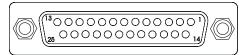

| Figure 4-4  | Standard DB 25-pin Connector – Front View.                              |        |

| Figure 4-5  | Micro Miniature DB 25-pin connector on DAS-429UNET/RTx-M – Front View   | 4-6    |

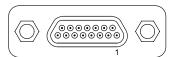

| Figure 4-6  | USB Communication Connector – Front View.                               | 4-8    |

| Figure 4-7  | USB Power Connector – Front View                                        |        |

| Figure 4-8  | Ethernet Connector – Front View.                                        |        |

| Figure 4-9  | External Signals Connector – Front View                                 |        |

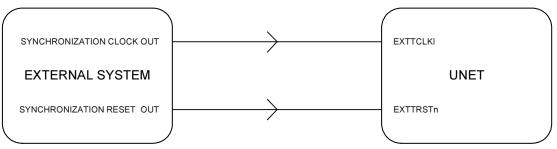

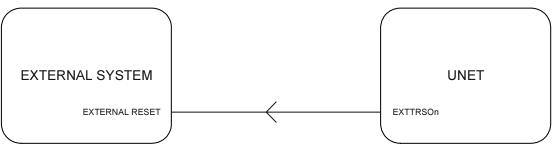

| Figure 4-10 | Synchronization of a Single DAS-429UNET/RTx Board to an External System |        |

| Figure 4-11 | Synchronization of an External System to a Single DAS-429UNET/RTx Board |        |

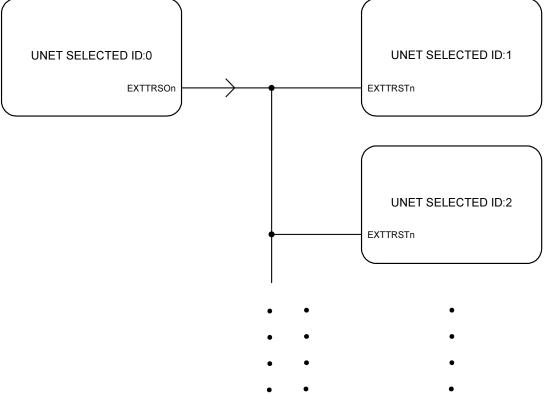

| Figure 4-12 | Synchronization Between DAS-429UNET/RTx Devices                         | . 4-12 |

| Figure 5-1  | Host Interface Global and IRIG B Registers Map                          |        |

| Figure 6-1  | Module Operation Flowchart                                              | 6-4    |

| Figure 6-2  | ARINC 429 Module General Memory Map                                     | 6-5    |

| Figure 6-3  | ARINC 429 Module Global Registers Memory Map                            |        |

| Figure 6-4  | Interblock Time Mode                                                    |        |

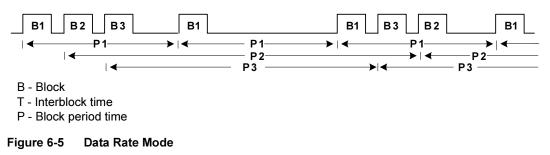

| Figure 6-5  | Data Rate Mode                                                          |        |

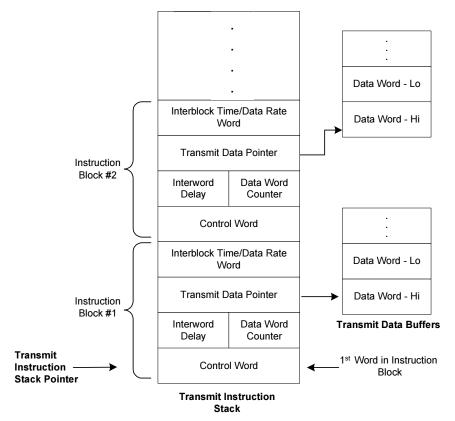

| Figure 6-6  | Transmit Instruction Stack Structure                                    |        |

| Figure 6-7  | Transmit Data Block.                                                    |        |

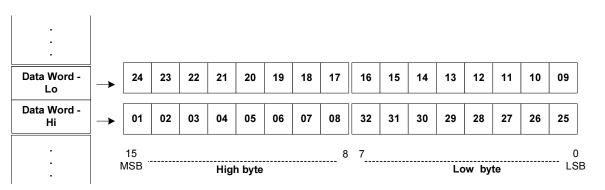

| Figure 6-8  | 32-Bit Transmit Data Words Format                                       |        |

| Figure 6-9  | 32-Bit Word Transmit Order Bit                                          | . 6-25 |

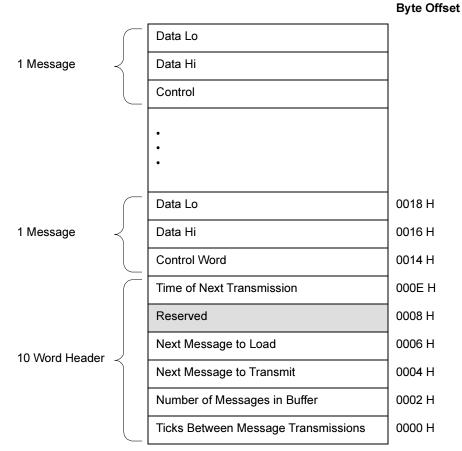

| Figure 6-10 | Buffer Structure                                                        | . 6-26 |

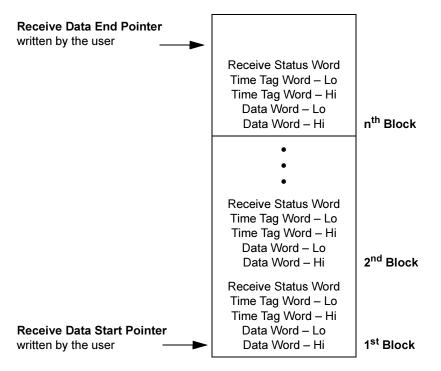

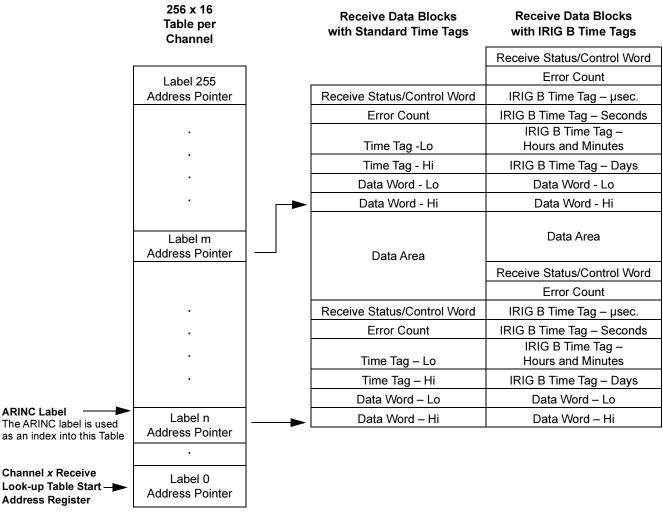

| Figure 6-11 | Receive Sequential Mode Buffer Structure with Standard Time Tags.       | 6-31   |

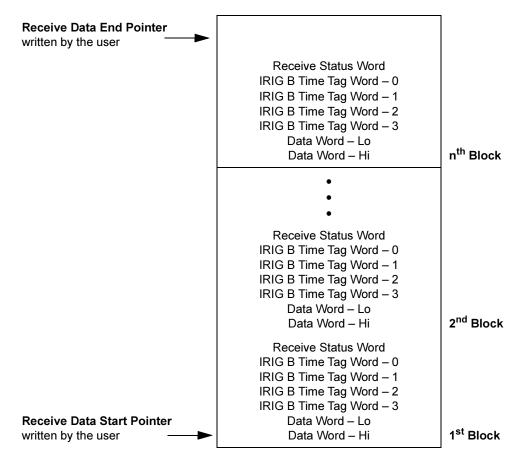

| Figure 6-12 | Receive Sequential Mode Buffer Structure with IRIG B Time Tags.         | . 6-31 |

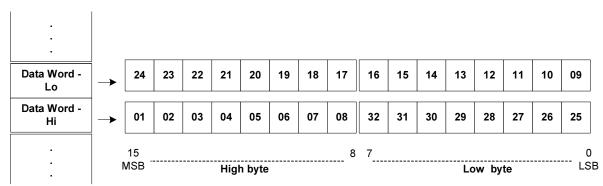

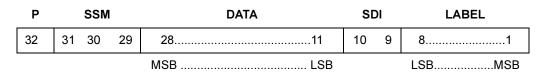

| Figure 6-13 | 32-Bit Receive Data Word Format                                         | . 6-32 |

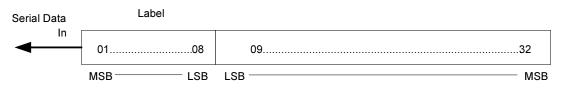

| Figure 6-14 | 32-Bit ARINC Word Order Bit                                             |        |

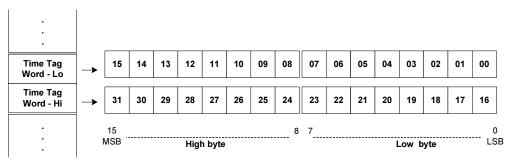

| Figure 6-15 | Time Tag Word Format in Standard (Non-IRIG B) Mode                      |        |

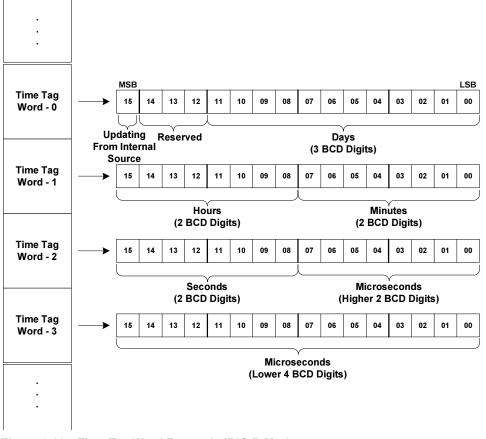

| Figure 6-16 | Time Tag Word Format in IRIG B Mode                                     | 6-33   |

| Figure 6-17 | Receive Sequential Mode Filter Table Diagram                            | . 6-35 |

| Figure 6-18 | Receive Look-up Table Structure                                         | . 6-36 |

| Figure 6-19 | Translation Table Entry                                                 |        |

| Figure 6-20 | Channel 0 Control Register Block Map                                    |        |

| Figure 6-21 | Channel 1 Control Register Block Map                                    | . 6-42 |

| Figure 6-22 | Channel 2 Control Register Block Map                                    | . 6-43 |

| Figure 6-23 | Channel 3 Control Register Block Map                                    | 6-44   |

| Figure 6-24 | Channel 4 Control Register Block Map                                    | 6-45   |

| Figure 6-25 | Channel 5 Control Register Block Map                                    | . 6-46 |

| Figure 6-26 | Channel 6 Control Register Block Map                                    |        |

| Figure 6-27 | Channel 7 Control Register Block Map                                    | 6-48   |

| Figure 6-28 | Channel 8 Control Register Block Map                                    | . 6-49 |

| Figure 6-29 | Channel 9 Control Register Block Map                                    | . 6-50 |

| Figure 7-1  | Discretes Control Registers Map                                         |        |

## Tables

## 1 Introduction

Chapter 1 provides an overview of the UNET.

| 1.1 | Overview                     | 1-2 |

|-----|------------------------------|-----|

|     | 1.1.1 Battery Option         | 1-3 |

| 1.2 | Block Diagram                | 1-3 |

| 1.3 | Product Features             | 1-4 |

| 1.4 | Supporting Software          | 1-5 |

| 1.5 | Discrete Channel Information | 1-6 |

| 1.6 | Technical Support            | 1-7 |

|     |                              |     |

Caution: Make sure there is no I/O communication while disconnecting any of the cables. Connecting or disconnecting the cables during communication can seriously damage the DAS-429UNET/RTx.

## 1.1 Overview

The DAS-429UNET/RTx is an intelligent, ARINC 429 interface device. Its small size and ability to interface through USB or Ethernet interfaces make it a complete solution for developing, testing and performing system simulation of the ARINC 429 bus, both in the lab and in the field.

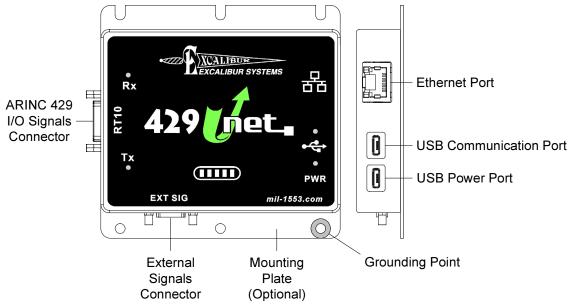

Figure 1-1 DAS-429UNET/RTx

#### Note:

- For an explanation of the LED indicators, see **4.2 LED Indicators** on page 4-4.

- For ordering information see Chapter 8: Ordering Information.

The DAS-429UNET/RTx supports up to ten ARINC 429 channels in any combination of transmitters and receivers. Each of these channels feature error injection and detection capabilities.

The receive channels allow for the storage of all selected Labels with status and Time Tag information appended to each word. The receivers allow for filtering and multi-storage modes of Data Words.

The transmit channels operate via a transmit 'instruction stack' which allows scheduling of data transmissions and reduces the need for host computer intervention.

In addition, this device provides IRIG B input and 8 Discrete I/O signals. The Discrete channel can record changes in the input Discrete with an associated Time Tag via a built-in FIFO. Output Discretes are open collector, capable of handling up to 32V with a maximum sink current of 100 mA each.

You can set for each Discrete:

- Whether it is input or output

- Input voltage level: TTL (0 5V) or Avionics (0 32V)

- · Whether to enable or disable debounce on inputs

Multiple *UNET*s can operate via USB ports on the same computer. In addition, multiple units can operate on the same network, by programming each one with a unique IP address, and can be accessed from any computer on the network.

The *DAS-429UNET/RTx* shares its API with the entire RTx family so that applications currently running on our PCIe, PCI, ExpressCard, or PCMCIA cards, will run without change on this device.

#### 1.1.1 Battery Option

The DAS-429UNET/RTx is available with an internal rechargeable battery. This allows the user to operate the DAS-429UNET/RTx without the need for any external power source. The internal battery can also be used as an auxiliary power source that can provide the additional power required for high data transmission conditions where external power sources are limited, for example, when the external power is provided by a host laptop computer. In this case, the internal battery can be used to minimize the amount of power drawn from the laptop's battery, which could be a critical requirement in the field where an external power supply is not readily available. For more information, see **4.4.1 Battery Information (Battery Option Only)** on page 4-13.

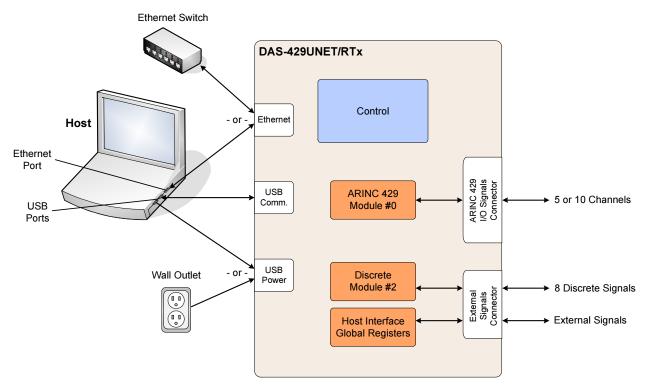

## 1.2 Block Diagram

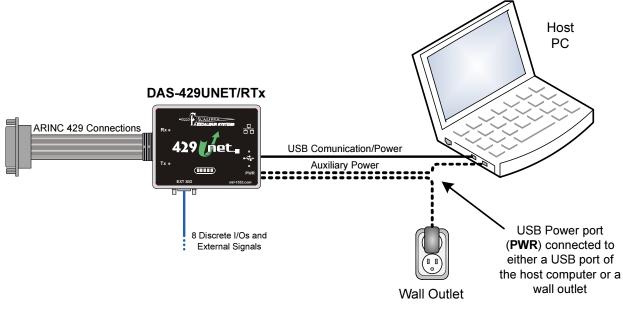

Figure 1-2 shows a block diagram of the DAS-429UNET/RTx. For information on connecting the cables, see **2.2 Connecting the Cables** on page 2-2.

Figure 1-2 DAS-429UNET/RTx Block Diagram

## 1.3 Product Features

#### **General Features**

- 5 or 10 ARINC 429 channels, each programmable as receive or transmit

- Memory mapped, 64K x 8 dual-port RAM

- Programmable Hardware Trigger Output

- Interrupt and Polling modes of operation

- Programmable (per channel):

- Buffer size

- Bit rates (Hi, Lo, Programmable)

- Parity (Odd, Even, On, Off)

- 8 Discrete I/O signals

- Smart power management

- Power source: Computer USB ports, USB power supply

- Mechanical configuration options:

- Mounting plate

- Hard-wired ARINC 429 I/O flat cable or panel mounted connector

#### **Transmit Channel Features**

- Transmit Modes

- Interblock Time

- Data Rate

- FIFO Data

- Transmit Features

- Transmit Sync Time (between Words)

- One-shot, N-times or Loop transmission

#### • Transmit Error Injection per Block

- Bit Count Hi/Lo

- Sync Time

- Stretch Bit

- Bit Rate (frequency)

- Parity

#### **Receive Channel Features**

- Receive Modes

- Look-up Table

- Sequential per channel

- Sequential Merge Mode (stores data from all Receive channels in one buffer)

- Receive Features

- Receive Features

- Word Status Tagging

- Word Time Tagging (32-bit) or IRIG B Time Tagging (64-bit)

- IRIG B input (standard IRIG B120 serial time code)

- Label/Data Filtering

- Start Triggers

- Receive Error Count per channel

- Receive Count Interval Trigger

#### Receive Error Detection per Word

- Bit Count

- Sync Time

- Parity

- Bit Coding Error

#### **Physical Characteristics**

- Dimensions: 98.5mm x 76mm x 18mm (not including connectors)

- Weight (/RT10 basic configuration, w/o battery): 180g

#### Software Support

- Software Tools: Advanced API with C source code. The Software Tools are available for several operating systems. See the Downloads section of our website.

- *Exalt Plus*: Excalibur Analysis Laboratory Tools for Windows (optional)

#### **Operating Environment**

- Operating Temp: -40° to + 75°C

- Humidity:

- 5% 90% noncondensing

- MTBF (/RT10): 157,500 hours at 25°C, G<sub>F</sub>, S217F

#### **Host Interface**

- Selectable USB 2.0 or 100Mbps Ethernet

- Power for /RT5 (max.): +5V @ 750 mA

- Power for /RT10 (max.): +5V @ 1000 mA

## 1.4 Supporting Software

The *UNET* has the following supporting software:

- *Excalibur Software Tools* Advanced API functions written in C language that enable you to write application and diagnostic programs. For more information, see **Chapter 3: Developing Applications**.

- Mystic A Windows test and simulation program for ARINC 429 bus communications data. Mystic can be from our website. Go to www.mil-1553.com, click Downloads, and then click Applications.

- Discrete Generator A Windows program that enables you to configure the Discrete channels on your Discrete module, run the module and view the status of incoming Discretes. You can also configure and monitor interrupts based on status of each Discrete channel. For more information, see

2.8 Running the Discrete Generator on page 2-29.

- *Exalt Plus (Excalibur Analysis Laboratory Tools)* An andvanced Windows program that enables you to monitor and analyze bus activity in real-time; to record bus activity that you can replay later (even when no modules are present and the computer is not connected to the bus); and to simulate bus activity by transmitting data over the bus. This program is an optional add-on to your purchase. For more information contact an Excalibur sales representative. See **1.6 Technical Support** on page 1-7.

## **1.5** Discrete Channel Information

The following sections describe the Discrete voltage/current levels and configuration.

#### **Discrete Channel Configuration**

The input voltage level and debounce setting for each input Discrete are set in the Discretes Configuration Registers, see **Discretes Configuration Registers** on page 7-12, or via the *M4KDiscrete Software Tools*, see the *M4KDiscrete Software Tools* Programmer's Reference.

The following sections provide more information about input and output Discretes.

#### Input Discrete Voltage Levels

Input Discretes can operate at either TTL or Avionics voltage levels, as defined in the following table.

| Voltage    |                                 | Value                                 |

|------------|---------------------------------|---------------------------------------|

| 0V-0.8V    | =                               | Logic 0                               |

| 2V – 5V    | =                               | Logic 1                               |